Architecture des micro calculateurs -Étude des microcontrôleurs STM32-

2016-2017

Dr. Sofiene Saidi Maitre assistant à l’ISTIC

1

Architecture des micro calculateurs

21h cours – 21h TD

Cours I. Les ARMs-CORTEX II. STM32F4 III. Les périphériques IV. Les protocoles

Atelier I. Installation et mise en œuvre II. GPIO-LCD III. ADC IV. USART V. Timers

2

Architecture des micro calculateurs -Étude des microcontrôleurs STM32-

Chapitre 1 Les Processeurs ARMs

3

Un microcontrôleurs:

Les microcontrôleurs 32 bits

4

Un microcontrôleurs:

Les microcontrôleurs 32 bits

Evolution des ventes en % des microcontrôleurs 8, 16 et 32 bits

5

Evolution des ventes des cœurs 32 bits pour les applications embarquées

6

Introduction

Introduction

-ARM(Advanced Risc Machines): une société UK a été créée en 1990. ARM conçoit des architectures des processeurs et vend leur licence sous forme d’IP(intellectual Property).

-Plus de 240 microcontrôleurs basés sur l’architecture ARM existent disponibles auprès d’une grande variété de constructeurs

-Les fabricants des microcontrôleurs et les processeurs, à base du coeur ARM, vendent annuellement plus que 2 billions de circuits.

7

La famille des ARM Cortex comprend 3 séries : ARM cortex-A : Applications Processeurs pour des OS et des applications utilisateurs complexes, supportent le jeu d’instruction ARM, Thumb et Thumb-2 ARM Cortex-R : Processeurs pour les systèmes temps réel, supportent le jeu d’instruction ARM, Thumb et Thumb-2 ARM Cortex-M : Optimisé pour les application bas-cout, supporte le jeu d’instruction Thumb- 2 uniquement

8

ARM-CORTEX

ARM-CORTEX

9

ARM-CORTEX

La performance d’une CPU est exprimée en Million d’Instructions Par Seconde (MIPS) ou Drysthone MIPS (DMIPS). Drysthone est le nom d’un benchmark très populaire dans les microcontrôleurs. Un benchmark est un programme de test spécialement conçu pour mesurer les performances d’une CPU. Plus généralement on exprime cette performance relativement à la fréquence d’horloge de la CPU cela permet une comparaison entre plusieurs architectures de CPU. Un autre paramètre important pour les systèmes embarqués est l’efficacité énergétique exprimée en mW/MHz.

Performance du cœur ARM cortex M3 = 1,25 DMIPS / MHz avec une efficacité énergétique de 0,19 mW / MHz : haute performance combinée avec une faible consommation c’est la caractéristique des cortex M3.

10

Pourquoi le Cortex-M3 ?

- Coût: En effet, le critère primordial qui incitait les développeurs de systèmes embarqués à opter pour les MCUs 8 bits était le prix. Avec le Cortex-M3, les prix des MCUs 32 bits a considérablement baissé et sont pratiquement dans le même ordre que les MCUs 8 bits.

- Efficacité énergétique: Les MCUs, comme tous les processeurs embarqués et à usage général, sont connus pour être flexibles au prix d’une consommation élevée en énergie de l’ordre de 1 à 3 MIPS/mW. Avec Cortex-M3, on atteint une efficacité de 12,5 MIPS/mW (figure). En plus, il supporte des modes basse consommation et permet une activation sélective des périphériques à utiliser.

Efficacité énergétique ( en MIPS/mW ) pour différentes plateformes embarquées

11

Pourquoi le Cortex-M3 ?

- Performance: Avec une capacité de traitement de 12,5 DMIPS et une fréquence de fonctionnement qui peut atteindre la valeur de 275 MHz, les performances du CortexM3 dépassent largement celles des architectures 8 et 16 bits (figure).

- Utilisation optimale de la mémoire: Grâce à l’utilisation de la technologie Thumb-2 qui permet l’utilisation simultanée d’instructions 16 et 32 bits, une meilleure densité du code est obtenue relativement aux autres architectures (figure 7)..

Comparaison de la densité du code du Cortex-M3par rapport à d’autres architectures

12

Pourquoi le Cortex-M3 ?

- Adaptation au temps réel (RT): Ceci est assuré par l’intégration d’un contrôleur d’interruptions gérant les priorités et le sauvegarde du contexte matériellement ce qui permet d’avoir une réponse déterministe et rapide aux événements externes. En plus, le Cortex-M3 intègre dans son jeu d’instructions, quelques unes qui s’exécutent d’une manière atomique.

- Débogage puissant: Grâce à un module de débogage intégré dans le cœur Cortex-M3 et qui permet de fixer un certain nombre de Breakpoints et watchpoints.

13

Pourquoi le Cortex-M3 ?

Industry Standard:

14

Le Cœur Cortex-M3

Le Cœur Cortex-M3:

- C’est un processeur 32 bits.– Un chemin de données (data path) 32 bits

– Un banc de registres 32 bits – Des interfaces mémoires de 32 bits.

- Un pipeline à 3 étages (Fetch, Decode et Execute)

- Une architecture Harvard

- Espace d’adressage du Cortex-M3 peut atteindre la taille de 4 GO.

- Jeu d’instruction thumb-2.

- NVIC = Nested vectored Interrupt controller

- Division et multiplication hardware 32 bits

- RTOS, noyau temps réel

- Mode basse consommation

- Debug via liaison JTAG

15

-Cela évite le goulot d’étranglement des architectures Von Neumann à un seul bus data + code. -Les performances sont encore accrues avec un circuit DMA (Direct Memory Access) qui permet l’accélération des transferts notamment de mémoire à mémoire. 16

Le Cœur Cortex-M3

Le cortex M3 dispose d’une architecture Harvard à 3 bus : 1) CODE ou I_CODE comme instruction code 2) CST ou D_CODE comme data code 3) DATA ou SYSTEM

Le Cœur Cortex-M3

Thumb-2:

Les premiers cœurs ARM7 et ARM9 utilisaient 2 jeux d’instructions distincts : 1) Thumb (pouce) : jeux d’instruction sur 16 bits favorisant la densité de code 2) ARM (bras) : jeux d’instruction sur 32 bits favorisant la performance

Le cortex M3 a vu apparaître un nouveau jeu d’instruction Thumb-2 qui est un compromis entre les jeux d’instructions précédents (ARM-32bits-+Thumb- 16bits-)

17

Le Cœur Cortex-M3

D’après ARM, il permet d’optimiser l’utilisation de l’espace mémoire sans dégrader les performances puisqu’on n’est plus obligé de basculer entre modes de fonctionnement (voir figure ).Des benchmarks réalisés donnent une performance de 1,2 DMIPS/MHz, c’est-à-dire le Cortex- M3 exécute, en moyenne, une instruction en moins d’un cycle horloge (1/1,2 = 0,833 cycle) .

A part l’amélioration des performances, une partie importante de ce nouveau jeu d’instructions Thumb-2 a été spécialement conçue pour être la cible des compilateurs. En plus, des instructions ont été introduites pour permettre :

- des divisions matérielles (SDIV et UDIV) qui nécessitent de 2 à 3 cycles horloge.

- des multiplications 32 bits qui se déroulent en un cycle horloge. 18

Le Cœur Cortex-M3

Organisation de la mémoire: Le processeur Cortex-M3 étant un cœur standard pour les microcontrôleurs, il possède une mémoire organisée d’une façon prédéterminée. La mémoire occupe un espace d’adressage de 4GO ( 2^32) réparti comme suit

Firmware : code nécessaire agissant à très bas niveau (Driver) et permettant aux applications d’utiliser le matériel d’une façon transparente Espace utilisé pour adresser les périphériques du CortexM3 : Contrôleur d’interruption, le Timer système, le bloc de contrôle, etc

Espace utilisé pour adresser les périphériques ajoutés par le constructeur du microcontrôleur intégrant le CortexM3.

Espace utilisé pour stocker les données relatives au code.

Espace utilisé pour stocker du code exécutable. On peut également stocker des données. 19

Le Cœur Cortex-M3

Gestion de la mémoire:

Other support data

Core unaligned does not ARM supports data SRAM Cortex-M3 that utilization unaligned can improve Long (32)

Long (32) Long (32)

Long (32) short (16)

short (16)

short (16) short (16)

Char Char Char

Char Data on boundaries

word aligned Char Char Char Char

Unused (wasted) space

Free space Can be used

Reduces SRAM Memory Requirements By Over

50%

20

Le Cœur Cortex-M3

21

Le Cœur Cortex-M3

- Un contrôleur d’interruptions NVIC(Nested Vector Interrupt Controller) supportant une entrée non masquable (NMI: No MaskableInterrupt), 14 sources d’interruptions internes générées par le noyau et les périphériques du Cortex-M3 et jusqu’à 240 sources d’interruptions externes.

- Un système de débogage qui permet de placer des points d’arrêt « Breakpoints» et d’observation «Watchpoints» matériels, ainsi que le traçage des instructions.

- Une unité de protection de mémoires(MPU: Memory Protection Unit) qui permet de déterminer des droits d’accès des applications à des zones mémoires définies. Cette unité est optionnelle et n’est pas disponible dans tous les processeurs Cortex-M3.

- Un Bus de matrice(AHB Bus Matrix: Advanced High Performance Bus) permettant de multiplexer les bus code et données vers 3 bus de sorties (I-Code, D-Code et System). Il permet également d’assurer l’alignement des données.

22

Le Cœur Cortex-M3

Modes opératoires du Cortex-M3

Une application embarquée déployée sur un microcontrôleur ( ou tout système embarquée) est constituée d’un ensemble de bouts de codes. Ces bouts de codes peuvent être : – Exécutés suite au déclenchement d’une interruption (événement). Dans ce cas, on parle de gestionnaire

d’interruption (Interrupt Handler ) ou de Routine d’interruption (ISR: Interrupt Service Routine). – Exécutés en fonction de l’évolution de l’état du système (code de démarrage dans main( ), tâches utilisateur en arrière plan, etc..). Ainsi, et en fonction du type de code exécuté, le Cortex-M3 se trouve dans l’un de deux modes : Mode « Handler» : Quand le processeur exécute des Handlers d’interruptions. Mode « Thread»: quand le processeur exécute des programmes, autres que les Handlers (programme principal, tâches utilisateur).

Après le démarrage, le Cortex-M3 exécute main ( ) et est par défaut en mode Thread. Le passage en mode Handler se fait automatiquement quand un Handler est exécuté suite au éclenchement d’une interruption. A la fin de l’exécution d’un Handler, le Cortex-M3 retourne en mode Thread

23

Le Cœur Cortex-M3

Modes opératoires du Cortex-M3

Le Cortex-M3 peut attribuer aux applications, en fonction de l’état du bit 1 du registre de contrôle (control [1]), deux niveaux de privilège: Niveau « Privileged» si control [1] = 0 : le programme peut utiliser toutes les instructions et peut accéder à toutes les ressources du processeur. Niveau « Unprivileged» si control [1] = 1: Une application ayant ce niveau a un certain nombre de limites : elle ne peut accéder au Timer System (SysTick), au contrôleur d’interruptions (NVIC) ni aux registres de contrôle du système. En plus, si le Cortex-M3 intègre un MPU, l’accès à certaines zones mémoires peut être interdit à ces applications.

Quand le Cortex-M3 est en mode handler, les codes exécutés ont toujours le niveau «privileged», indépendamment de la valeur du bit du registre de contrôle.

Quand le Cortex-M3 est en mode thread les codes exécutés peuvent avoir le niveau «privileged» ou « unprivileged», en fonction de la valeur du bit 1 du registre de contrôle.

24

La famille STM32

ST-Microelectronics a proposé toute une famille de microcontrôleurs 32 bits basée sur le cœur Cortex-M3

Architecture générique d’un microcontrôleur à base du cœur Cortex-M3

25

La famille STM32

La famille des microcontrôleurs ST est baptisée STM32, c’est une famille qui se compose de sept séries de microcontrôleurs: F4, F3, F2, F1, F0, L1 et W. Chaque série est basée sur soit un Cortex-M4, CortexM3, ou un Cortex-M0 . Le processeur Cortex-M4F est conceptuellement un Cortex-M3 en plus de DSP (Digital Signal Processor) et d’instructions de virgule flottante simple précision.

26

STM32Fw0 x y z

STM32F407VG??

W :Série( 1,2,3,4) X: désigne la catégorie à laquelle appartient le μcY:désigne le nombre de pins ainsi que le type de package du circuit intégré (T: 36 pins, C: 48 pins, R : 64 pins, V : 100 pins et Z : 144 pins). Z: la taille de la mémoire flash interne (4 pour 16 Kbytes, 6 pour 32Kbytes, 8 pour 64 Kbytes, B pour 128 Kbytes, C pour 256 Kbytes, D pour 384 Kbytes , E pour 512 Kbytes et G pour 1Mbytes)

STM32F4

27

STM32F4-discovery

28

STM32F4

Système d’horloge: Ces différents bus, composants et périphériques fonctionnent avec des fréquences d’horloge synthétisées à partir de l’un des deux signaux horloge suivants : – HSI(High Speed Internal) : Il s’agit d’un signal de fréquence 8 Mhz généré par un oscillateur interne intégré au niveau du μc. C’est cette fréquence qui est utilisée par défaut après une opération de reset. Elle présente l’inconvénient de manque de précision et de stabilité. – HSE(High Speed External) : Il s’agit d’un signal de fréquence comprise entre 4 et 40 Mhz, généré par un dispositif (à base d’un cristal) placé à l’extérieur du μc. Il est à noter que deux périphériques (Watch Dog et le Real Time Clock RTC) fonctionnent avec un signal d’horloge différent et de faible fréquence qui peut être soit généré localement par un oscillateur interne (~ 32 Khz, non précis) appelé LSI(Low Speed Internal) ou bien à partir d’un dispositif externe appelé LSE(Low Speed External) et devant produire une fréquence de 32,768 Khz. Alimentations: La carte STM32 génère plusieurs tensions :

- DMV= 2,0 à 3,6 V: Alimentation externe pour les E/S et le régulateur interne.

- VDDA= 2,0 à 3,6 V: Alimentations externes analogiques pour ADC, blocs de réinitialisation, PLL. VDDA et AHPV doit être connecté à VDD et VSS, respectivement.

- VBAT= 1.8 à 3.6 V: Alimentation pour RTC lorsque la DMV n’est pas présent.

29

STM32F4

Modes basse consommation: la STM32 prend en charge trois modes basses consommations pour atteindre le meilleur compromis entre faible consommation d’énergie, à court temps de démarrage et de réactivation de la source.

- Sleep mode: (mode veille), seul le CPU est à l’arrêt. Tous les périphériques continuent de fonctionner et peut réveiller le CPU quand une interruption ou un événement se produit.

- Stop mode: réalise la plus faible consommation de puissance tout en conservant le contenu de SRAM et des registres. Toutes les horloges dans le domaine 1,8 V sont arrêtés, le PLL, le HSI RC et les oscillateurs à cristaux HSE sont désactivés. Le régulateur de tension peut aussi être mis soit en mode normal ou en mode de faible puissance.

- Standby mode: utilisé pour atteindre la plus faible consommation de puissance. Le régulateur de tension est éteint. Le PLL, le HSI RC et les oscillateurs à quartz HSE sont également éteint. Après être entré en mode veille, la SRAM et le contenu du registre sont perdues, sauf pour les registres de sauvegarde La mode de l’appareil sort de veille quand une remise à zéro externe, une réinitialisation IWDG, un front montant sur la broche WKUP, ou une alarme RTC se produit.

30

STM32F4

DMA (Direct Memory Access) Des données peuvent être échangées entre la mémoire centrale et les circuits périphériques sans intervention du CPU pour alléger son fonctionnement. Le DMA (en français, Accès Direct à la Mémoire), un sous-système indépendant du CPU, va transférer les données du périphérique vers la mémoire (entrée), de la mémoire vers le circuit périphérique (sortie), entre mémoires ou entre périphériques. Le DMA peut être utilisé avec les principaux périphériques: SPI, I2C, ADC,USART, toutes les minuteries et les ADC..

RTC (horloge temps réel) – registres de sauvegarde La carte STM32 possède dix registres de sauvegarde de 16-bit utilisés pour stocker les données de l’application utilisateur lorsque la puissance DMV n’est pas présente. L’horloge temps réel fournit un ensemble de compteurs fonctionnant en permanence, qui peuvent être utilisés avec un logiciel approprié pour fournir une fonction de calendrier d’horloge, et une interruption d’alarme. Le RTC dispose d’un compteur 32 bits programmable pour la mesure à long terme en utilisant un registre de comparaison pour générer une alarme. Un diviseur de 20 bits est utilisé pour générer une base de temps de 1 seconde à partir d’une horloge à 32,768 kHz.

31

STM32F4-périphériques-

RCC Reset and Clock Control PWR Power control GPIO General Purpose Input Output EXTI External Inetrrupt RTC Real Time Clock WDG watchdog SPI Serial Peripheral Interface I2C Inter-Integrated Circuit DMA Direct Memory Manager Flash Embedded Flash memory TIM Advanced-control Timers ADC Analog-to-Digital Converter DAC Digital -to-AnalogConverter

32

STM32F4-périphériques-

SPI

I2C

33 STM32F407VG

RS-232

Architecture des micro calculateurs -Étude des microcontrôleurs STM32-

Chapitre 2 Les microcontrôleurs STM32F4 -Entrées Sorties GPIO du STM32-

2016-2017

34

-GPIO-

– La commande – L’acquisition – La communication

- La STM32 dispose de pins (broches) permettant de véhiculer les signaux électriques du microcontrôleur vers l’extérieur (Sortie ou Output) et de l’extérieur vers le microcontrôleur (Entrée ou Input) : on parle d’Entrées-sorties à usage général (GPIO: General Purpose Inputs Outupts).

- Ces entrées-sorties (IO) sont regroupées en ports de 16 IO. Dans un stm32F407VG, on trouve GPIOA(16), GPIOB(16), GPIOC(16), GPIOD(16), GPIOE(16), GPIOH(2)

Chaque port GPIO possède son propre signal d’horloge et contient des registres de contrôle qui déterminent le mode de fonctionnement des pins ainsi que des registres permettant de lire l’état binaire des pins en entrée et d’imposer l’état des pins en sortie.

35

Ces pins sont également reliés aux différents périphériques du microcontrôleur (USART, Timer, ..) à travers l’AFIO(Auxiliary Function Input Output). L’AFIO permet de multiplexer les connexions entre pins et périphériques. Il offre ainsi une flexibilité au niveau du choix du pin à utiliser pour véhiculer un signal donné. Quand l’AFIO est désactivé, les connexions par défaut entre pins et périphériques sont établies. Une fois l’AFIO activé, il est possible de remapper (multiplexer) les pins

-GPIO-

36

-GPIO-

37

Architecture d’un port GPIO:

- Les IO du STM32 sont de type Five Volt Tolerant (FT), c’est-à-dire qu’ils peuvent supporter une tension d’entrée de 5V sans dommage ou dysfonctionnement.

-GPIO-

38

-GPIO-

- Un registre d’entrées (Input Data Register : IDR) de 32 bits. Les 16 bits poids faible étant utilisés pour la lecture des valeurs logiques issues des 16 pins du port.

- Un registre de sorties (Output Data Register : ODR) de 32 bits. Les 16 bits poids faible étant utilisés pour imposer les valeurs logiques au niveau des 16 pins du port.

- Un registres de Mise à 1 ( Bit Set Reset Register : BSRR) et un registre de remise à 0 et (Bit Reset Register : BRR). Par le biais de ces registres, il est possible de changer l’état d’un ou plusieurs bits du registre ODR, et par conséquent les sorties GPIOs, en en un seul cycle : on parle d’accès atomique

- 2 registres de configuration (Control Register High /Low : CRH/CRL) permettant de déterminer le sens, le mode de fonctionnement et la fréquence de commutation des GPIOs. A cette fin, 4 bits sont utilisés pour chaque IO, et donc 64 bits (4*16) pour la totalité des 16 IOs d’un GPIO. D’où la nécessité d’utiliser 2 registres de 32 bits.

- Un registre de verrouillage de la configuration (Configuration Locking Register) utilisé pour interdire la modification du contenu des registres de configuration (CRH et CRL) sauf après un reset. Ceci protège contre les manipulations involontaires et les perturbations électromagnétiques.

- A l’initialisation, tous les IO sont configurés en ‘Input Floating’.

39

-GPIO-

40

-GPIO-

41

1

RCC->AHB1ENR = 0x0008;

Impossible d’afficher l’image.

Impossible d’afficher l’image.page283

10 0 1 10 0 1

GPIOD->MODER =0x55000000;

-GPIO-

42

GPIOD->OTYPER = 0xF0000000;

-GPIO-

43page283

GPIOD->ODR = 0x0000F000;

LED_ON

44page284

44page284

GPIOD->ODR = 0x00000000;

GPIOD->PUPDR = 0x00000000;

LED_OFF

-GPIO-

44page284

44page284

-GPIO-

#include « stm32f4xx.h » int i ; int main(void) {void delay (void) { for (i =0;i <100000; i++); /* only to delay for LED flashes */

LED_Initialiser ();

while(1)

{

LED_ON(); delay(); }LED_OFF();

void LED_Initialiser (void) { RCC->AHB1ENR = 0x0008; //IO PortD clock enable /

GPIOD->MODER =0x55000000; //Set GPIOD 12/13/14/15 as outputs PIN

delay(); } }

GPIOD->OTYPER = 0xF0000000; //Set output as Push-Pull mode GPIOD->OSPEEDR = 0x00000000; //Set output speed 2MHz low speed GPIOD->PUPDR = 0x00000000; //Set no pull up and pull down

}void LED_ON (void) { GPIOD->ODR = 0x0000F000; }void LED_OFF (void) { GPIOD->ODR = 0x00000000; }

45

Pour faciliter l’utilisation des fonctionnalités offertes par les périphériques des microcontrôleurs STM32 et accélérer le développement des applications, ST fournit La librairie « STM32Yxxx_StdPeriph_Driver » permettant un accès transparent à la partie matérielle du circuit (périphériques, contrôleur d’interruptions,). Cette librairie est censée respecter le standard de programmation appelé CMSIS (Cortex Microcontroller Software Interface Standard).CMSIS a été défini par ARM avec un ensemble de fabricants de circuits intégrés et de développeurs de compilateurs visant à faciliter le portage et la réutilisation des applications écrites en langage ‘C’ pour les microcontrôleurs se basant sur un cœur Cortex-M. Néanmoins, la portabilité des programmes, écrits en ‘C’, entre les microcontrôleurs à base du Cortex-M est loin d’être assuré

CMSIS

46

CMSIS

Couche d’accès aux périphériques noyau(Core Peripheral Functions ) : contient les définitions, les adresses et les fonctions d’ accès aux différents registres du CPU e t des périphériques du noyau (core peripherals) contenus dans Cortex même : le contrôleur d’interruptions NVIC, le timer système Systick, le bus matrix, etc. Ces définitions et fonctions se trouvent au niveau des fichiers core_M3.cet core_M3.h.

Le fichier de démarrage startup_stm32Yxxx .s, écrit en assembleur et qui permet de: – Initialiser les registres du CPU (Program Counter et Stack Pointer). – Installer La table des vecteurs d’interruptions. – Faire un saut vers main.c et donner la main à l’application utilisateur.

Couche d’accès aux périphériques hors noyau(Device Peripheral Functions): permettant une manipulation transparente des périphériques (port parallèle, série, Conversion A/N et N/A, Timer, etc..)

On trouve ainsi les fichiers ayant le format stm 32Yxxx_ppp.c et .h Chaque fichier étant relatif à l’un des périphériques du microcontrôleur (ppp étant remplacée par l’abréviation du périphérique). La liste suivante présente les principaux périphériques de la famille des microcontrôleurs STM32

47

CMSIS

48

CMSIS-Exercice

49

Exercice

Exercice 1 : Proposer un programme en C qui permet d’allumer une LED , connectée à PB7, en appuyant sur un bouton poussoir connecté à PC6

Exercice 2 : Ecrire un organigramme et le programme qui permet d’allumer une diode, parmi les 4 diodes connectées à PD12-13-14-15, à chaque appui sur le bouton PA0 d’une manière successive.

50

Horloge STM32F4

SystemCoreClock = ((INPUT_CLOCK (HSE_OR_HSI_IN_HZ) / PLL_M) * PLL_N) /PLL_P

Input Clock=8MHz MAX CLOCK =168MHz Exemple: PLL_M=2 PLL_N=300 PLL_P=2

→ SystemCoreClock=150MHz

51

Architecture des micro calculateurs -Étude des microcontrôleurs STM32-

Chapitre 3 Les microcontrôleurs STM32F4 -Convertisseur Analogique Numérique ADC du STM32-

2016-2017

52

ADC: convertisseur analogique numériqueSTM32F4xx ont jusqu’à 3 ADCs dont chaque a 19 canaux.

- 16 canaux externes, connectés aux broches E/S

- 3 canaux internes -Vbat: :Voltage on battery pin for RTC

– Temp sensor interne

-Vref : : référence de tension pour ADC

53

ADC: convertisseur analogique numériqueChannel ADC1 ADC2 ADC3

APB 2 2 2

ADC Channel 0 PA0 PA0 PA0

ADC Channel 1 PA1 PA1 PA1

ADC Channel 2 PA2 PA2 PA2

ADC Channel 3 PA3 PA3 PA3

ADC Channel 4 PA4 PA4 PF6

ADC Channel 5 PA5 PA5 PF7

ADC Channel 6 PA6 PA6 PF8

ADC Channel 7 PA7 PA7 PF9

ADC Channel 8 PB0 PB0 PF10

ADC Channel 9 PB1 PB1 PF3

54

ADC: convertisseur analogique numériqueADC Channel 10 PC0 PC0 PC0 ADC Channel 11 PC1 PC1 PC1 ADC Channel 12 PC2 PC2 PC2 ADC Channel 13 PC3 PC3 PC3 ADC Channel 14 PC4 PC4 PF4 ADC Channel 15 PC5 PC5 PF5

55

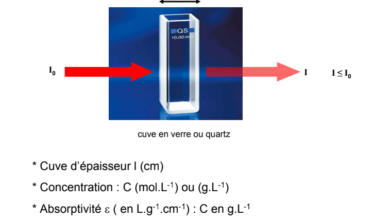

ADC: convertisseur analogique numérique

Caractéristiques:

– Résolution sur 12-bit

- Modes: Single mode, Independent mode,

-ADC-

MODES

56

void ADC1_Configuration(void) {ADC_CommonInitTypeDef ADC_CommonInitStructure;

ADC_InitTypeDef ADC_InitStructure;

ADC_CommonInitStructure.ADC_Mode = ADC_Mode_Independent; ADC_CommonInitStructure.ADC_Prescaler = ADC_Prescaler_Div2; ADC_CommonInitStructure.ADC_DMAAccessMode = ADC_DMAAccessMode_Disabled;

ADC_CommonInitStructure.ADC_TwoSamplingDelay = ADC_TwoSamplingDelay_5Cycles; ADC_CommonInit(&ADC_CommonInitStructure);

-ADC-

ADC_InitStructure.ADC_Resolution = ADC_Resolution_12b; ADC_InitStructure.ADC_ScanConvMode = DISABLE; ADC_InitStructure.ADC_ContinuousConvMode = ENABLE; ADC_InitStructure.ADC_ExternalTrigConvEdge = ADC_ExternalTrigConvEdge_None; ADC_InitStructure.ADC_ExternalTrigConv = ADC_ExternalTrigConv_T1_CC1; ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right; ADC_InitStructure.ADC_NbrOfConversion = 1;

ADC_StructInit(&ADC_InitStructure);

ADC_Init(ADC1, &ADC_InitStructure); ADC_RegularChannelConfig(ADC1, ADC_Channel_x, 1, ADC_SampleTime_144Cycles); ADC_EOCOnEachRegularChannelCmd(ADC1, ENABLE);

ADC_Cmd(ADC1, ENABLE); }

-ADC-

intget_ADCValue() {ADC_SoftwareStartConv(ADC1);

while(ADC_GetFlagStatus(ADC1, ADC_FLAG_EOC) == RESET); valeur_ADC= ADC_GetConversionValue(ADC1); }

-ADC-

Architecture des micro calculateurs -Étude des microcontrôleurs STM32-

Chapitre 4 Les microcontrôleurs STM32F4 -Transmission Série USART du STM32-

2016-2017

60

USART

La liaison série asynchrone (UART) permet d’envoyer et de recevoir des données à l’aide d’une ligne d’émission (TXD) et d’une ligne de réception (RXD). Cette interface est couramment utilisée pour établir un dialogue entre le μC et un ordinateur. Dans ce cas il faut prévoir une adaptation des niveaux entre l’ordinateur (Norme RS232) et le μC (Signaux compatibles TTL).

En l’absence de transmission, les lignes TXD et RXD se trouvent au niveau logique haut.

Format de transmission :

– 1 bit de start : Front descendant puis niveau « 0 » pendant la durée de transmission d’un bit. – 8 ou 9 bits de données : Bit de poids faible transmis en 1er . – 1 bit de stop : niveau « 1 » pendant la durée de transmission d’un bit.

61

La vitesse de transmission de l’émetteur doit être identique à la vitesse d’acquisition du récepteur. Ces vitesses sont exprimées en BAUDS (1 baud correspond à 1 bit / seconde, dans notre cas). Il existe différentes vitesses normalisées: 9600, 4800, 2400, 1200… bauds

USART

62

USART-STM32F4

Pins pack 1 Pins pack 2 Pins pack 3

U(S)ARTx TX RX TX RX TX RX APB

USART1 PA9 PA10 PB6 PB7 2

USART2 PA2 PA3 PD5 PD6 1

USART3 PB10 PB11 PC10 PC11 PD8 PD9 1

UART4 PA0 PA1 PC10 PC11 1

UART5 PC12 PD2 1

USART6 PC6 PC7 PG14 PG9 2

63

void init_usart(void){

GPIO_InitTypeDef GPIO_InitStructure; USART_InitTypeDef USART_InitStructure;

RCC_APB1PeriphClockCmd(RCC_APB1Periph_USART2, ENABLE); RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA, ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP ; GPIO_Init(GPIOA, &GPIO_InitStructure);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource2, GPIO_AF_USART2);

USART_InitStructure.USART_BaudRate = 9600; USART_InitStructure.USART_WordLength = USART_WordLength_8b; USART_InitStructure.USART_StopBits = USART_StopBits_1; USART_InitStructure.USART_Parity = USART_Parity_No; USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None; USART_InitStructure.USART_Mode = USART_Mode_Tx; USART_Init(USART2, &USART_InitStructure); USART_Cmd(USART2, ENABLE); // enable USART2

}

Configuration USART

64

Utilisation de l’USART

void USART_puts(volatile char *s){

while(*s){

while( !(USART2->SR & 0x00000040) ); USART_SendData(USART2, *s); *s++; }}

USART_SendData(USARTx,msg);

65

Utilisation de l’USART

Câble

Wifi

Bleutooth

USART-USB

66

Architecture des micro calculateurs -Étude des microcontrôleurs STM32-

Chapitre 5 Les microcontrôleurs STM32F4 -Les Timers TIM du STM32-

2016-2017

67

Les timers (TIM)

Le STM32F407VG dispose de 14 timers.

Timer Type Resolution Prescaler Channels MAX TIMER

CLOCK* APB

TIM1, TIM8 Advanced 16bit 16bit 4 SysClk 2 TIM2, TIM5 General purpose 32bit 16bit 4 SysClk,

SysClk/2 1

TIM3, TIM4 General purpose 16bit 16bit 4 SysClk,

SysClk/2 1

TIM9 General purpose 16bit 16bit 2 SysClk 2

TIM10, TIM11 General purpose 16bit 16bit 1 SysClk 2

TIM12 General purpose 16bit 16bit 2 SysClk,

SysClk/2 1

TIM13, TIM14 General purpose 16bit 16bit 1 SysClk,

SysClk/2 1

TIM6, TIM7 Basic 16bit 16bit 0 SysClk,

SysClk/2 1

68

Les timers (PWM)

69

Les timers (PWM)

void TIMER_Init(void) { TIM_TimeBaseInitTypeDef TIM_BaseStruct; RCC_APBxPeriphClockCmd(RCC_APB1Periph_TIM4, ENABLE); TIM_BaseStruct.TIM_Prescaler =0; TIM_BaseStruct.TIM_CounterMode = TIM_CounterMode_Up; IM_BaseStruct.TIM_Period = 8401; TIM_BaseStruct.TIM_ClockDivision = TIM_CKD_DIV1;

TIM_BaseStruct.TIM_RepetitionCounter = 0; TIM_TimeBaseInit(TIM4, &TIM_BaseStruct); TIM_Cmd(TIM4, ENABLE); }

void PWM_Init(void) { TIM_OCInitTypeDef TIM_OCStruct; TIM_OCStruct.TIM_OCMode = TIM_OCMode_PWM2; TIM_OCStruct.TIM_OutputState = TIM_OutputState_Enable; TIM_OCStruct.TIM_OCPolarity = TIM_OCPolarity_Low;

TIM_OCStruct.TIM_Pulse = xxxxx TIM_OC1Init(TIMx, &TIM_OCStruct); TIM_OC1PreloadConfig(TIMx, TIM_OCPreload_Enable);

timer_tick_frequency = 84000000 / (TIM_Prescaler + 1)

TIM_Period = timer_tick_frequency / PWM_frequency – 1

pulse_length = ((TIM_Period + 1) * DutyCycle) / 100 – 1

70

Les timers (PWM)

void GPIO_Init(void) { GPIO_InitTypeDef GPIO_InitStruct;

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOx, ENABLE); GPIO_PinAFConfig(GPIOD, GPIO_PinSource12, GPIO_AF_TIMx);

GPIO_InitStruct.GPIO_Pin = GPIO_Pin_12; GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF; GPIO_InitStruct.GPIO_OType = GPIO_OType_PP; GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_NOPULL; GPIO_Init(GPIOD, &GPIO_InitStruct); }

int main(void) {

GPIO_Init();

TIMER_Init();

TPWM_Init();

while (1) {

}

71

Channel 1 Channel 2 Channel 3 Channel 4

PP1 PP2 PP3 PP1 PP2 PP3 PP1 PP2 PP3 PP1 PP2 PP3

TIM 1 PA8 PE9 PA9 PE10 PA10 PE13 PA11 PE14

TIM 2 PA0 PA5 PA15 PA1 PB3 PA2 PB10 PA3 PB11

TIM 3 PA6 PB4 PC6 PA7 PB5 PC7 PB0 PC8 PB1 PC9

TIM 4 PB6 PD12 PB7 PD13 PB8 PD14 PB9 PD15

TIM 5 PA0 PH10 PA1 PH11 PA2 PH12 PA3 PI0

TIM 8 PC6 PI5 PC7 PI6 PC8 PI7 PC9 PI2

TIM 9 PA2 PE5 PA3 PE6

TIM 10 PB8 PF6

TIM 11 PB9 PF7

72

Référence

- Cours systèmes embarqués Mr Dermergi Amir INSAT

- Datascheet STM32F4..

- www.st.com

73

télécharger gratuitement Architecture des micro calculateurs -Étude des microcontrôleurs STM32-